Product Summary

The BS62LV1027SI-55 is a high performance, very low power CMOS Static Random Access Memory. The BS62LV1027SI-55 is organized as 131,072 words by 8 bits and operates from a wide range of 2.4V to 5.5V supply voltage. Advanced CMOS technology and circuit techniques provide both high speed and low power features with a typical CMOS standby current of 0.1uA at 3V/25℃ and maximum access time of 55ns at 3V/85℃. Easy memory expansion is provided by an active LOW chip enable (CE1), an active HIGH chip enable (CE2), and active LOW output enable (OE) and three-state output drivers.

Parametrics

BS62LV1027SI-55 absolute maximum ratings: (1)VTERM, Terminal Voltage with Respect to GND: -0.5 to Vcc+0.5 V; (2)TBIAS, Temperature Under Bias: -40 to +85℃; (3)TSTG, Storage Temperature: -60 to +150℃; (4)PT, Power Dissipation: 1.0 W; (5)IOUT, DC Output Current: 20 mA.

Features

BS62LV1027SI-55 features: (1)Wide Vcc operation voltage: 2.4V to 5.5V; (2)Very low power consumption; (3)High speed access time: -55 to 55ns; -70 to 70ns; (4)Automatic power down when chip is deselected; (5)Easy expansion with CE2, CE1, and OE options; (6)Three state outputs and TTL compatible; (7)Fully static operation; (8)Data retention supply voltage as low as 1.5V.

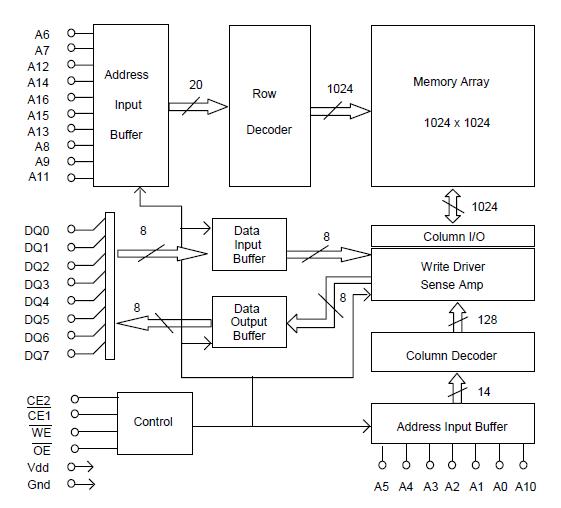

Diagrams

|

BS62LV1023DC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

BS62LV1023DI |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

BS62LV1023JC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

BS62LV1023JI |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

BS62LV1023PC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

BS62LV1023PI |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))